In passato la rilevazione dei fronti si è effettuata tramite codice VHDL come

In cui non veniva richiesto l’utilizzo di alcuna libreria ed il funzionamento abbastanza semplice era pensato per il tipo nativo di dato BIT.

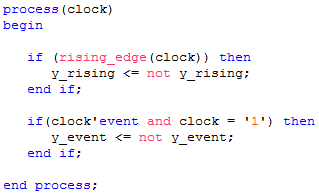

La libreria IEEE.STD_LOGIC_1164 introduce assieme al tipo STD_LOGIC le funzionalità rising_edge e falling_edge così definite:

Cosa cambia nella pratica tra l’utilizzo delle nuove funzioni e il vecchio modo di rilevare fronti?

Purtroppo sulla rete sono spesso presenti imprecisioni o informazioni incomplete che non coprono tutta la possibile casistica di casi.

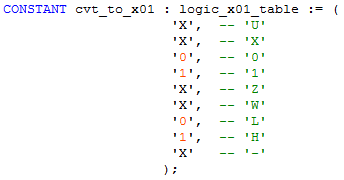

Per capirlo dobbiamo analizzare alcune funzioni, di particolare importanza per la comprensione del codice la funzione To_X01 sotto riportata:

Questa funzione a sua volta si affida ad una “tabella” per effettuare una conversione dal tipo std_ulogic ai soli valori X, 0 ed 1.

Le funzioni rising_edge e falling_edge gestiscono quindi in modo diverso l’intera casistica dei 9 possibili valori assunti dal tipo std_logic.

Il fronte di salita sarà scatenato solamente quando il valore precedente convertito in X01 sarà 0, ovvero solamente durante le transizione dal valore logico 0 o L al valore 1 convertito in X01, quindi effettivamente al valore logico 1 o H. Analoghe considerazioni per il fronte di discesa.

Per chiarificare vediamo un semplice esempio:

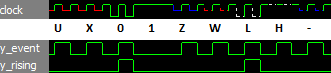

Con la relativa simulazione

In cui è possibile notare il differente comportamento nel passaggio dai vari stati logici al valore logico 1, mentre col vecchio codice si ha sempre (a parte giustamente nel passaggio da 1 a 1 in cui non c’è un fronte) un effettivo fronte di salita, con la funzione rising_edge non viene invece scatenato in alcuni casi per una migliore corrispondenza tra hardware sintetizzato e simulato.

Concludendo consiglio sempre di utilizzare le nuove funzioni rising_edge e falling_edge per i nuovi progetti.

![stdlogic2[4] stdlogic2[4]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEgusfCF37vZH5jmLbGKDa1o1ZwVYpyDvSWVOApOTZR70R8kLfctpXklP8Dd5-XAYuMIiHXryuiAirQ8Q9pQd5ssdDIQzG_TZdAZEUe6Fay8nxgyXB73i6vvDFgykITevYYv78jXYxSonsQ/rw/?imgmax=800)