Questo articolo vuole essere una collezione di risorse per iniziare lo studio dei circuiti integrati di casa Cypress, precisamente gli IC della serie FX2LP.

Qualora fosse necessario disporre di comunicazione USB 2.0 Hi-Speed (480 MBps) e di un microcontrollore ad 8 bit ad elevate prestazioni, IC come CY7C68013A (sotto è mostrato il suo diagramma a blocchi logico) che utilizzeremo nell’articolo sono sicuramente da valutare.

Notiamo come sul dispositivo in considerazione non sia presente una memoria Flash o EEPROM interna per la memorizzazione del firmware, da un punto di vista produttivo significa ridurre di molto l’area di silicio e quindi il costo del dispositivo non dovuto solo alla area della memoria ma anche alla pompa di carica (Charge Pump) interna necessaria per la generazione della elevata tensione necessaria per il suo utilizzo.

La pompa di carica introduce problemi legati alla miniaturizzazione del dispositivo ed influisce spesso sulla scelta del processo produttivo, di contro per la memorizzazione del firmware sarà necessaria una memoria esterna o il caricamento del firmware in memoria RAM al collegamento del PC tramite USB, scelta perseguita in diversi prodotti commerciali che rende allo stesso tempo molto semplice l’aggiornamento del firmware.

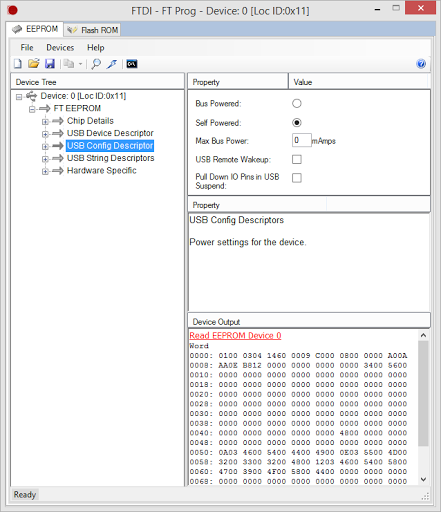

E’ possibile utilizzare una EEPROM esterna da 16 bytes come l’IC 24LC00 per la sola memorizzazione del VID/PID USB associato al dispositivo in modo da far associare subito il driver desiderato al dispositivo.

Il micro nell’IC è compatibile a livello di codice binario con gli 8051 classici e permette di riutilizzare toolchain e strumenti come Keil uVision C51 per lo sviluppo del codice. E’ necessario prestare attenzione ad alcuni dettagli in quanto la maggiore velocità (4 clock / istruzione) rispetto all’architettura classica (12 clock / istruzione) può introdurre differenze nelle tempistiche di funzionamento. Nel panorama Open Source è disponibile il compilatore SDCC (Small Device C Compiler).

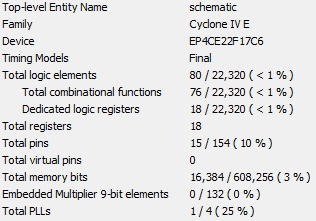

Sulla rete sono disponibili diverse schede di sviluppo per tutte le tasche, dalle economiche schede amatoriali CY7C68013A MINI BOARD ai kit di sviluppo ufficiali come il CY3684 EZ-USB FX2LP Development Kit contenente al suo interno oltre all’IC anche SRAM, GAL, IO Expanders, diverse EEPROM, Transceiver, e molto altro ancora.

Per quanto riguarda la programmazione non è necessario comperare un programmatore esterno in quanto grazie alla interfaccia USB è possibile caricare il firmware da PC nella RAM o nella EEPROM collegata all’IC.

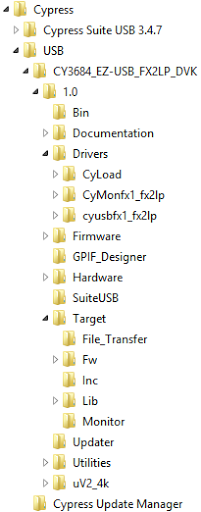

Per iniziare, anche nel caso di schede di sviluppo economiche, installiamo il software di sviluppo CY3684 EZ-USB FX2LP Development Kit che creerà diverse cartelle nel nostro disco.

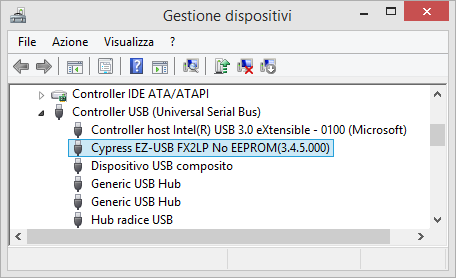

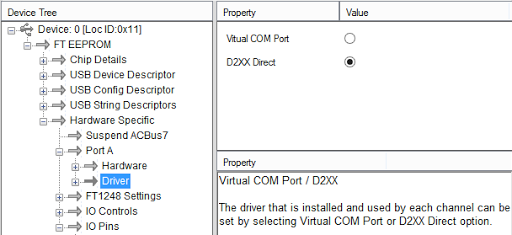

In particolare è importante la cartella Drivers\cyusbfx1_fx2lp in quanto sarà necessario installare il driver ivi contenuto al collegamento del dispositivo al PC tramite USB. Dopo l’installazione del driver verrà identificato come Cypress EZ-USB FX2LP No EEPROM e sarà pronto per l’interfacciamento coi tools di sviluppo.

Apriamo la Cypress USB Console, installata assieme al Development Kit per verificare che il driver del dispositivo sia correttamente installato

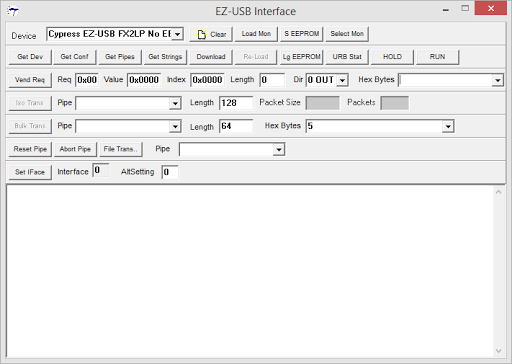

Scegliendo Options / EZ-USB Interface è possibile accedere ad altri comandi per il caricamento di firmware (pulsante Download per il caricamento del firmware nella RAM), scrittura della EEPROM collegata al dispositivo (pulsante S/Lg EEPROM per la scrittura di piccole o grosse memorie EEPROM, S = Small, Lg = Large) ed altro ancora.

L’interfaccia del programma non è purtroppo molto user-friendly, è consigliato consultare la guida EZ-USB Development Kit User Guide per maggiori informazioni sugli strumenti di Cypress.

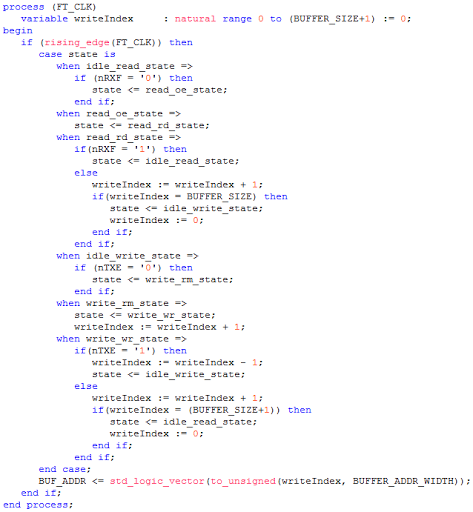

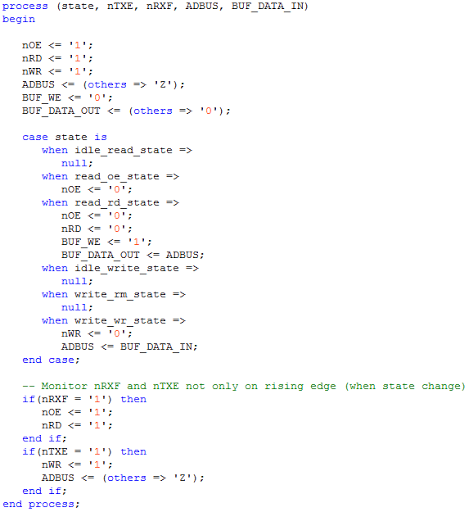

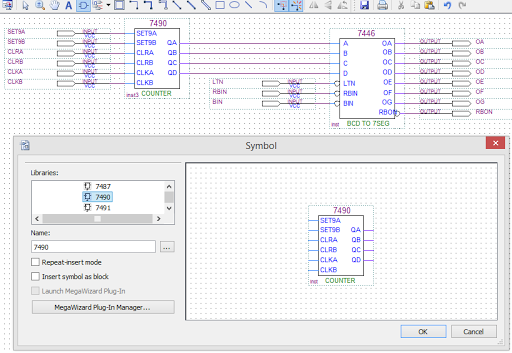

Realizziamo adesso un semplice programma programmando il microcontrollore 8051.

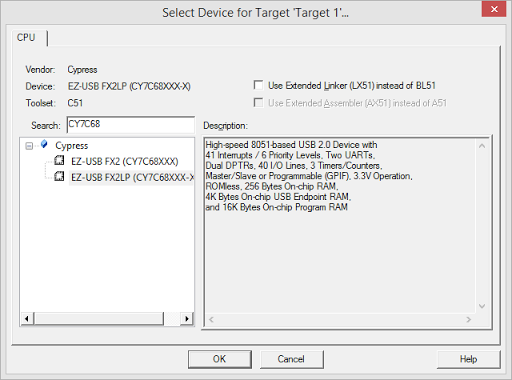

Apriamo Keil uVision5, disponibile anche in versione di valutazione gratuita con qualche limitazione, e scegliamo Project / New uVision Project indicando il percorso del nostro progetto. Ci verrà chiesto il dispositivo da programmare, scegliamo EZ-USB FX2LP (CY7C68XXX-X) e premiamo OK.

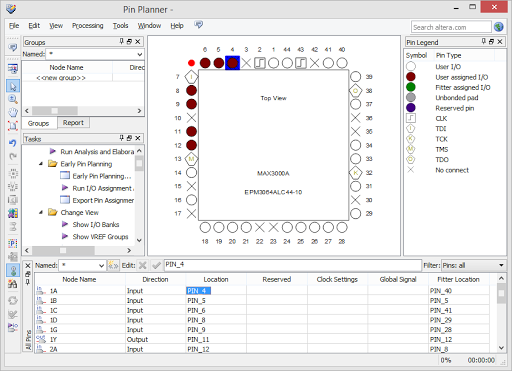

Scegliamo adesso Projects/Options for Target e dalla scheda Target impostiamo la frequenza di clock del cristallo della nostra scheda di sviluppo

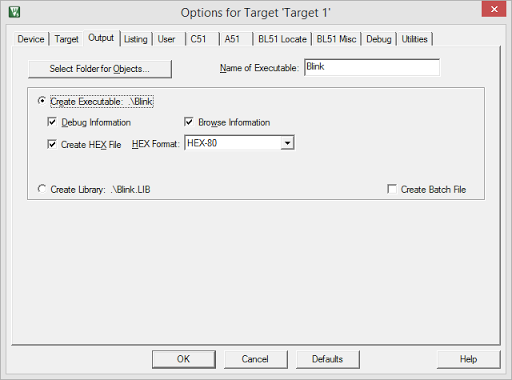

Nella scheda Output assicuriamoci che sia abilitata la creazione del file HEX

Nella scheda Utilities infine impostiamo come strumento di programmazione del dispositivo il percorso del programma CyUpload, scaricabile al termine dell’articolo, che ho sviluppato tramite le libreria Cypress CyUSB .NET DLL di cui parleremo eventualmente in un successivo articolo, per semplificare, integrare e velocizzare la programmazione ed evitare di ricorrere al programma Cypress USB Console ogni volta.

Nel campo Arguments inseriamo la stringa %H che sarà trasformata automaticamente nel percorso del file HEX durante la programmazione da parte di Keil uVision.

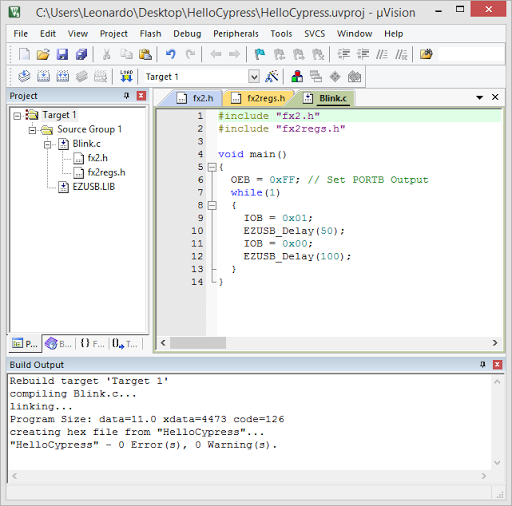

Adesso che il progetto è stato correttamente configurato, aggiungiamo al progetto nel Source Group 1 la libreria EZUSB.LIB dal percorso C:\Cypress\USB\CY3684_EZ-USB_FX2LP_DVK\1.0\Target\Lib\LP per poter utilizzare funzioni come EZUSB_Delay() per l’attesa di un certo numero di millisecondi.

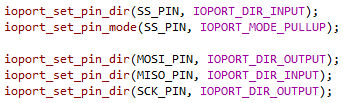

Creiamo adesso un nuovo file Blink.c col seguente codice:

Dove OEB è il registro della porta B adibito alle direzioni dei pin (1 = Output, 0 = Input) ed IOB è il registro di I/O per la lettura e scrittura dei bytes.

Il codice mostrato alzerà il pin PB0 ad HIGH per 50ms e lo porterà a LOW per 100ms, ripetendo il codice ciclicamente.

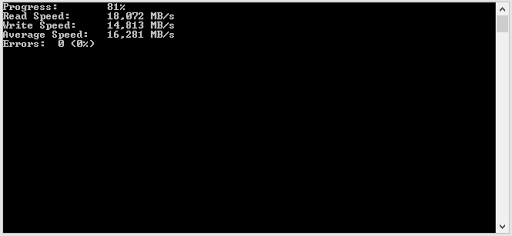

Una volta terminata la stesura del codice è possibile compilare il programma con il comando Project / Build target e caricarlo nel dispositivo tramite il comando Flash / Download

Variando i tempi di lampeggio e collegando un led con relativa resistenza sarà possibile creare il classico Hello World del mondo della programmazione firmware.

Abbiamo visto in questo articolo alcuni strumenti e un esempio di programmazione dei dispositivi Cypress,

L’Application Note Getting Started with FX2LP può fornire un’introduzione preliminare alternativa, il punto di inizio per lo studio del microcontrollore e delle funzionalità USB dell’IC è il manuale di riferimento tecnico EZ-USB Technical Reference Manual ed il datasheet del dispositivo.

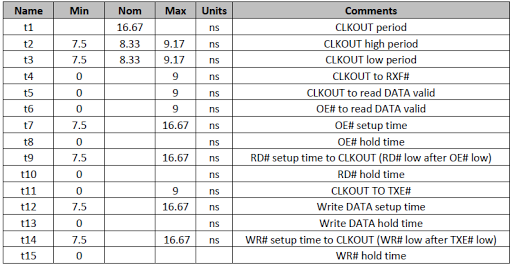

E’ possibile continuare il proprio studio esplorando funzionalità avanzate come l’USB Hi-Speed, i GPIF, e tanto altro ancora.

Importante: Il programma CyUpload è una utility pensata per l’uso personale e non ampiamente testata per funzionare in tutte le condizioni possibili. Programma la RAM del primo dispositivo utilizzante i driver Cypress trovato, è necessario collegare solamente il dispositivo Cypress da programmare o utilizzare Cypress USB Console che può essere utilizzato per controllare se sono presenti altri dispositivi Cypress collegati.

Buon divertimento con i circuiti Cypress