In questo articolo (vedi precedente) illustriamo il funzionamento dell’IC FT232H per poterlo così interfacciare alla nostra scheda FPGA DE0-Nano

L’FT232H permette di eseguire due tipi di operazione nella modalità FT245 sincrona: operazione di lettura ed operazione di scrittura.

Operazione di lettura

Un’operazione di lettura può iniziare quando il chip porta il pin RXF#, che quindi andrà monitorato, a LOW. L’FPGA può portare il pin OE# a LOW per far presentare il primo byte sul bus (i pin ADBUS) dopodiché può portare il pin RD# a LOW per informare il chip dell’avvenuta lettura. Tenendo il pin RD# a LOW si possono leggere sequenzialmente più dati, o si può interrompere la lettura portando ad HIGH il segnale RD#.

Sul fronte di salita del clock (pin ACBUS5) saranno presentati i sequenzialmente gli ulteriori dati. Una volta letti tutti i dati disponibili il segnale RXF# verrà portato ad HIGH dal chip.

NB: E’ importante monitorare sia sul fronte di salita sia di discesa il segnale RXF# per poter portare ad HIGH i pin OE# ed RD# al primo fronte di salita del clock nel caso il segnale RXF# venga portato ad HIGH nel fronte di discesa precedente, come illustrato nel diagramma.

Operazione di scrittura

Un’operazione di scrittura può essere iniziata quando il pin TXE# è LOW. WR# deve essere portato a LOW quando i dati presentati sul bus sono validi. Una scrittura sequenziale può essere fatta ad ogni fronte di salita del clock mentre TXE# è ancora LOW. La FPGA deve monitorare TXE# per assicurarsi che i dati possano essere accettati. Sia TXE# che WR# devono essere LOW per far si che i dati vengano accettati.

NB: Così come nell’operazione di lettura è importante monitorare sia sul fronte di salita sia di discesa il segnale TXE# per poter portare ad HIGH il pin WR# al primo fronte di salita del clock.

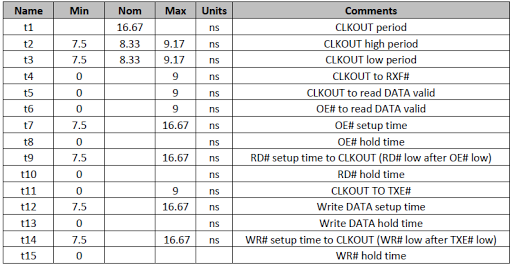

Tempistiche

E’ estremamente importante rispettare le seguenti tempistiche

Per assicurarsi che la FPGA rispetti i vincoli temporali sarà necessario impostare i vincoli tramite un file SDC (Synopsys Design Constraints) ed impostare ragionevolmente il carico capacitivo dei pin tramite Quartus.

Sotto è riportato un esempio di file SDC con in particolare i vincoli di Setup ed Hold Time

Diagramma a blocchi del sistema di LoopBack

Per illustrare meglio sia la lettura che la scrittura realizzeremo un semplice loopback, ovvero la ricezione e la ri-trasmissione di dati tramite USB 2.0.

Il clock fornito dal chip FT232H viene utilizzato anche per la logica interna, per migliorare l’aderenza alle tempistiche è introdotto preliminarmente in un PLL dove è possibile tramite sfasamento migliorare i tempi di Setup o di Hold.

Il sistema è composto da due blocchi principali: ft232h_loopback che contiene la vera logica del sistema, implementata tramite macchina a stati finiti, ed il blocco single_port_ram, una semplice memoria SRAM implementata direttamente su FPGA il cui scopo è memorizzare i dati letti durante la fase di scrittura. La memoria funge da buffer per migliorare le prestazioni del sistema ed evitare di scrivere il dato subito dopo ogni byte letto.

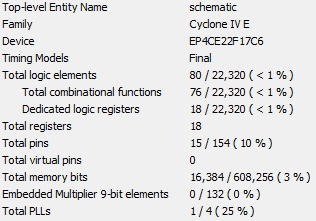

La dimensione del buffer è personalizzabile senza modificare il codice dei blocchi ma semplicemente cambiando il valore dei parametri associati, nell’immagine è presente un buffer di 2KB (2048 bytes) pari a 16384 bit, il 3% della memoria integrata nella FPGA della DE0-Nano.

Macchina a stati finiti

La macchina a stati finiti implementata nel blocco ft232h_loopback è molto semplice e sotto illustrata graficamente

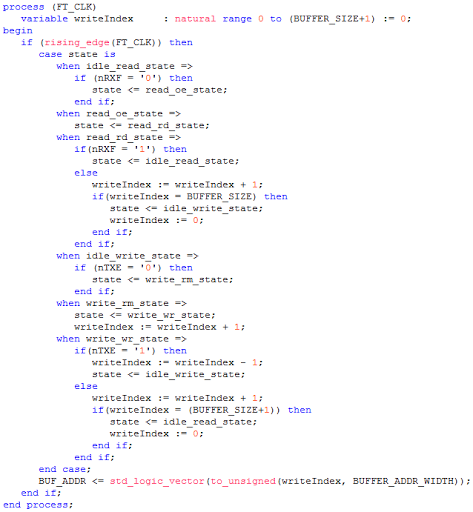

Il processo che determina lo stato successivo, basato sullo stato corrente e sugli ingressi è il seguente:

Dove writeIndex rappresenta l’indirizzo della SRAM dove avverrà la lettura o la scrittura

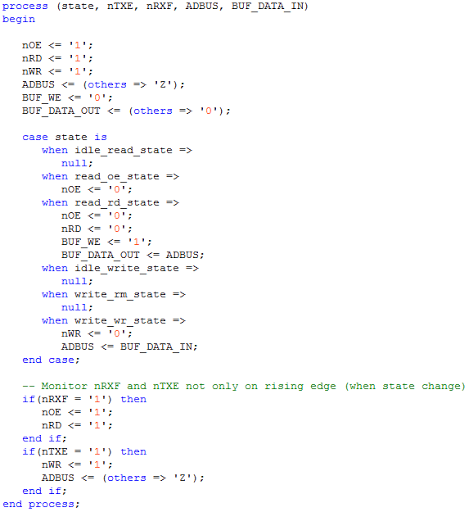

Il processo che determina le uscite in base allo stato corrente e agli ingressi è il seguente

Da notare l’utilizzo dell’alta impedenza sul bus durante la lettura. Essendo il processo non dipendente dal clock il monitoraggio dei segnali nRXF ed nTXE avviene correttamente, congruamente a quanto detto precedentemente.

Memoria RAM

L’implementazione della memoria RAM è quella classica, realizzata a partire dai template predefiniti di Quartus

Presenta parole di lunghezza 1 byte mentre la dimensione della memoria è impostata tramite il parametro generico ADDR_WIDTH.

L’utilizzo di risorse finale del sistema così implementato è molto ridotto e lascia spazio all’implementazione di altre funzionalità sulla scheda

Per quanto riguarda la parte FPGA è tutto, vedremo nel prossimo articolo come realizzare il software per scrivere e leggere dati tramite USB 2.0 ed interfacciarci quindi alla scheda DE0-Nano ad altissima velocità.

Thank for your sharing. I tried to program the VHDL codes into modules and implement it on my FPGA with FT2232H on board. However, it cannot read accurately the bytes that were written. Looks like one byte lagging for two-bytes case.

RispondiEliminaAre timings constraints met during the compilation?

Elimina