Uno dei principali problemi in sistemi composti da FPGA e PC è stabilire una comunicazione semplice, veloce ed affidabile. Vediamo in questo articolo come aggiungere alla scheda di sviluppo DE0-Nano il supporto USB Hi-Speed (fino a 480 MBit/s teorici) per aprire nuovi scenari di sviluppo come l’acquisizione ed elaborazione di dati ad alta velocità.

La scheda di sviluppo DE0-Nano dispone di due pin header superiori da 40 pin (2x20) che permettono l’espansione della scheda.

Utilizzeremo l’header GPIO-1 per collegare la scheda di sviluppo UM232H basata sull’IC FT232H di FTDI che offre una comunicazione USB 2.0 tramite un’interfaccia FIFO sincrona ad 8 bit di semplice utilizzo che offre trasferimenti fino a 40 MBytes/s. Da prove pratiche in alcuni casi, sfruttando vari buffer, si sono misurate velocità di trasferimento addirittura superiori.

Sopra il diagramma a blocchi del chip FT232H, tra le altre funzionalità è possibile notare un buffer di 1K Bytes in ricezione e trasmissione

Lo schema del modulo di espansione è abbastanza semplice, non contiene elementi aggiuntivi e collega la scheda FPGA a quella USB 2.0 impostando tramite i collegamenti l’alimentazione del modulo UM232H in modalità self-powered, ovvero alimentata tramite la scheda DE0-Nano e non dalla porta USB.

Il consumo del modulo UM232H è molto contenuto, circa 60mA ma solamente quando collegato tramite USB al PC, rendendolo appetibile anche in applicazioni alimentate a batteria. A PC scollegato il consumo del modulo è non rilevante in quanto in stand-by grazie al pin PWRSAV#.

Sotto un’immagine del prototipo del modulo USB 2.0, realizzato tramite Toner Transfer, collegato alla scheda di sviluppo.

Configuriamo il modulo UM232H

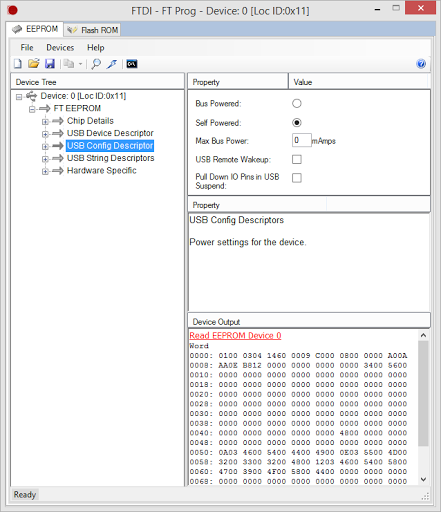

Una volta realizzato il modulo di espansione e collegato al PC tramite il programma FT Prog è possibile configurare la EEPROM a bordo dell’UM232H contenente le configurazioni del modulo.

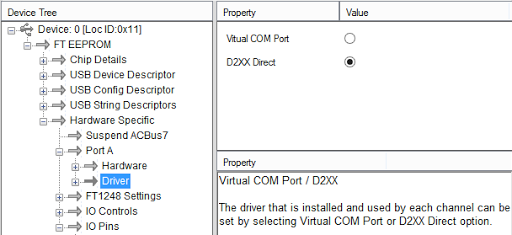

In particolar modo impostiamo nella pagina USB Config Desciptor il dispositivo come Self Powered, selezioniamo inoltre il canale come 245 FIFO ed il Driver come D2XX Direct come mostrato nelle seguenti immagini:

Il driver Virtual COM Port seppur permetta di sostituire senza sforzo vecchie porte seriali nei software dove previste non permette di raggiungere velocità elevate. D2XX offre un’API semplice ed efficiente, disponibile sia in C/C++ sia in linguaggi come C#.

Prossimamente vedremo come realizzare il software lato PC e come programmare la FPGA per realizzare una semplice applicazione di LoopBack (es. un file inviato alla FPGA e ritrasmesso al PC) al fine di verificare il funzionamento del tutto.

Vi lascio per il momento solamente un’altra immagine..

A presto

Tabella dei Ritardi di Propagazione (Modulo UM232H + Adattatore)

RispondiEliminaDi seguito è riportata la caratterizzazione fisica e temporale dei percorsi di segnale dall'FT232H fino ai pin della FPGA.

Il calcolo della lunghezza totale include:

Lo sbroglio interno del modulo commerciale UM232H.

Lo sbroglio dell'adattatore custom (singolo strato).

Una costante di 1.0 mm per il pin header di interconnessione.

Il tempo di volo (Ritardo Stimato) è calcolato assumendo un fattore di propagazione tipico per le tracce microstrip su strati esterni in FR4, pari a circa 6.0 ps/mm (150 ps/inch).

Segnale FT232H Pin FPGA UM232H (mm) Adattatore (mm) Header (mm) Lunghezza Totale (mm) Ritardo Stimato (ps)

AD1 (Data) GPIO_21 3.92 5.08 1.00 10.00 ~60 ps (Min)

AD0 (Data) GPIO_23 4.20 5.08 1.00 10.28 ~62 ps

AD2 (Data) GPIO_19 4.69 5.08 1.00 10.77 ~65 ps

AD3 (Data) GPIO_17 5.95 5.08 1.00 11.03 ~66 ps

AD4 (Data) GPIO_15 8.54 5.08 1.00 14.62 ~88 ps

AD5 (Data) GPIO_13 10.55 5.08 1.00 16.63 ~100 ps

AD6 (Data) GPIO_11 12.88 5.08 1.00 18.96 ~114 ps

AD7 (Data) GPIO_9 15.21 5.08 1.00 21.29 ~128 ps (Max Dati)

--- --- --- --- --- --- ---

AC7 (PWRSAV#) GPIO_... 9.27 17.34 1.00 27.61 ~166 ps

AC6 (OE#) GPIO_22 8.63 23.91 1.00 33.54 ~201 ps

AC4 (SIWU#) GPIO_20 9.67 24.96 1.00 35.63 ~214 ps

AC2 (RD#) GPIO_7 10.77 24.53 1.00 36.30 ~218 ps

AC1 (TXE#) GPIO_5 12.90 24.53 1.00 38.43 ~231 ps

AC3 (WR#) GPIO_6 9.52 28.12 1.00 38.64 ~232 ps

AC0 (RXF#) GPIO_3 23.06 24.53 1.00 48.59 ~292 ps

AC5 (CLKOUT) GPIO_IN0 4.40 48.75 1.00 54.15 ~325 ps

Nota di analisi temporale:

Come si evince dai dati, lo sbroglio del bus dati (AD0-AD7) presenta uno skew fisico massimo di circa 68 ps. Il segnale di clock (AC5), a causa della posizione sul pinout del modulo originale e del conseguente sbroglio sull'adattatore, subisce il ritardo di propagazione maggiore del sistema (~325 ps). I dati arrivano ai pin di destinazione mediamente oltre 200 ps prima del fronte di clock di riferimento.