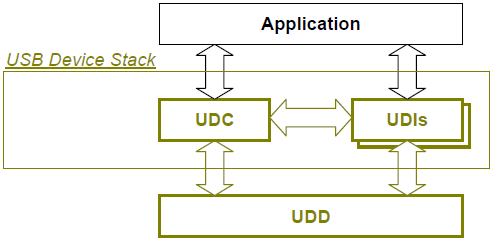

Precedentemente abbiamo parlato del chip di memoria AL422B, vediamo oggi come verificarne in prima battuta il corretto funzionamento tramite un design su logiche programmabili che simuli una scrittura di dati veloce ed una lettura più lenta dalla memoria FIFO.

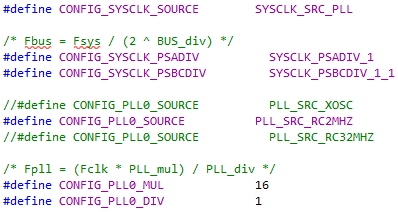

Nel nostro design avremo diversi domini di clock tutti derivati dal clock principale generato dall’oscillatore a 50 MHz presente sulla scheda che confineremo in distinte entità per evitare problematiche assai poco piacevoli e suddividere in parti più piccole il tutto.

Possono infatti nascere problemi durante l’analisi e sintesi con processi sensibili contemporaneamente a più fronti di salita all’interno di macchine a stati (es. costrutto VHDL case).

Abbiamo già parlato dell’entità SyncReset in precedenti articoli, riassumendo brevemente serve per rendere sincrona la de-asserzione del segnale reset cercando così di evitare stati metastabili.

L’entità AL422B_Reader simula la lettura dei dati e gestisce il reset della scrittura dei dati implementando una semplice macchina a stati scandita dal clock rck a 0.25 MHz (simulando ad esempio la lettura da parte di un lento microcontrollore) generato a partire dal clock a 50 MHz.

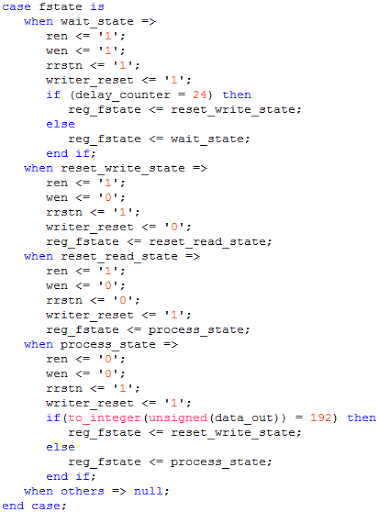

Al reset la macchina a stati parte dallo stato wait_state in cui vengono attesi 0.1ms per inizializzare il chip AL422B come descritto nel relativo datasheet prima di passare allo stato reset_write_state in cui viene riavviata la scrittura da parte dell’entità AL422B_Writer. Dopodiché si passa allo stato reset_read_state in cui viene resettato l’indice di lettura interno alla memoria per iniziare nello stato process_state la lettura dalla prima locazione di memoria. Una volta letto il valore 192 (scelto arbitrariamente) la lettura è ultimata e si passa nuovamente allo stato reset_write_state.

Sotto riportato un estratto della macchina a stati AL422B_Reader (alla fine dell’articolo il progetto è interamente scaricabile):

In cui è possibile notare la gestire dei segnali REn, WEn, RRSTn, writer_reset. In particolare è da notare che al reset della lettura della memoria tramite RRSTn il segnale REn è portato al livello logico alto (lettura disabilitata), come consigliato dall’ultima versione del datasheet e dall’articolo precedente.

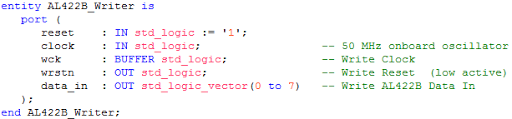

Passiamo all’entità AL422B_Writer così definita:

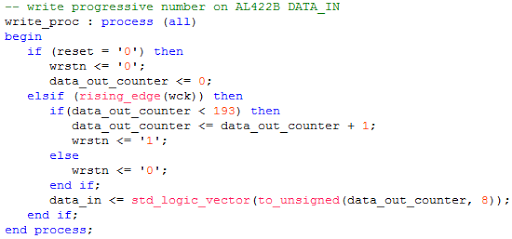

Analizziamo solamente il processo write_proc tralasciando la generazione del clock da 25 MHz ottenuta tramite un contatore. Il processo si occupa di scrivere sulla memoria FIFO tramite il bus ad 8 bit data_in i numeri progressivi da 0 a 192 per poi fermarsi fino alla riattivazione col segnale di reset che fa ripartire il conteggio.

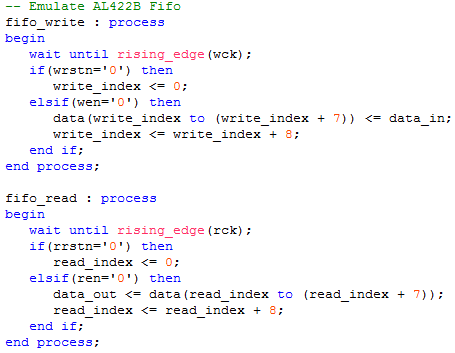

La verifica del codice tramite la sola simulazione richiede l’emulazione del chip AL422B, eseguibile ad esempio tramite dei processi fifo_write e fifo_read come

Che però andrebbero migliorati per imitare il perfetto comportamento del chip. Seguiamo in questo caso, anziché concentrarci sull’emulazione, una strada alternativa: utilizzeremo un analizzatori di stati logici per verificare a “runtime” il nostro progetto.

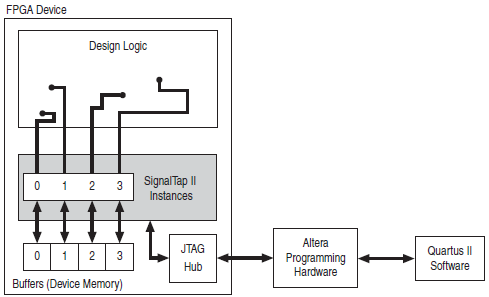

Quartus II include l’utilissimo tool SignalTap II Logic Analyzer (richiede l’attivazione del talkback, vedi precedente articolo per l’abilitazione) che permette di esaminare in tempo reale il comportamento dei segnali interni senza utilizzare pin aggiuntivi ma tramite l’interfaccia JTAG. Il circuito esterno composto dal chip AL422B con relativi condensatori bulk e di disaccoppiamento dovrà naturalmente essere collegato alla FPGA (con GND in comune) durante il debug con SignalTap.

Avremo quindi gratuitamente un analizzatori di stati logici virtuale con tanto di trigger, l’unico prezzo da pagare sarà in termini di risorse (LEs e memoria) sulla FPGA in quanto verrà caricato assieme al nostro design. Le risorse utilizzate dipenderanno dal numero di funzionalità e di campioni da memorizzare

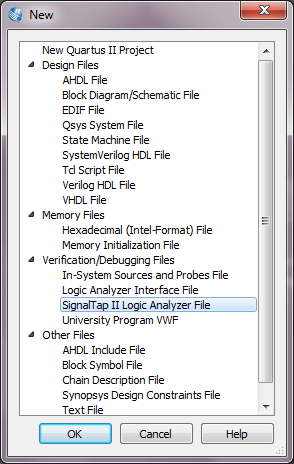

Creiamo innanzitutto un nuovo file SignalTap tramite il menù File / New scegliendo SignalTap II Logic Analyzer File

Apparirà l’interfaccia grafica del programma

Come prima cosa tramite il pulsante Setup scegliamo il nostro programmatore JTAG, dopodiché indichiamo tramite il pulsante sfoglia (i puntini …) sulla destra nella finestra Signal Configuration il segnale di clock che servirà a SignalTap per campionare gli altri segnali. Assicuriamoci che sia il segnale a frequenza maggiore per evitare la perdita di eventi, l’analisi delle tempistiche di Quartus riporterà la frequenza massima campionabile.

L’analizzatore logico campionerà i dati ad ogni fronte di salita, Altera raccomanda l’utilizzo di un segnale globale non gated di clock sincrono ai segnali da acquisire.

Premuto il pulsante sfoglia apparirà una finestra Node Finder che permetterà di scegliere un nodo dal nostro design. Scegliamo pre-synthesis nelle opzioni per visualizzare i nomi prima della sintesi e portiamo il pin clock nei nodi selezionati tramite un doppio click o selezionandolo e premendo il pulsante >.

I segnali pre-sintesi elencati esistono dopo l’elaborazione del design ma prima di ogni ottimizzazione di sintesi, se non si sta utilizzando la compilazione incrementale aggiungere solamente questa tipologia di segnali.

Sempre nella finestra Signal Configuration è possibile scegliere il numero di campioni da visualizzare al trigger impostando Sample depth, nell’Instance Manager in alto apparirà il corrispondente utilizzo di risorse e sarà possibile capire se il nostro dispositivo sarà in grado di contenere l’analizzatore con le impostazioni scelte risparmiandoci così eventualmente una compilazione con esito negativo.

Nell’immagine sopra la FPGA utilizzata dispone solamente di 26 blocchi di memoria di medie dimensioni, coi nodi selezionati da monitorare ed una profondità di 2K campioni (altre impostazioni di default) verranno utilizzati 15 blocchi (circa 56k bits) ed 828 LEs.

Nell’area centrale della finestra (nella scheda Setup) è possibile aggiungere tramite doppio-click i nodi da visualizzare e configurare eventuali trigger. Scegliendo Basic AND il trigger verrà valutato se tutte le condizioni impostate saranno verificate mentre scegliendo Basic OR basterà una sola delle condizioni per scatenare il trigger. Sono disponibili inoltre opzioni avanzati di Trigger che non vedremo in questo articolo.

Prima di iniziare il monitoraggio sarà necessario ricompilare il progetto e caricare nuovamente sulla FPGA il nostro design dopodiché tramite il pulsante Run Analysis (cerchiato in rosso nell’immagine seguente) al verificarsi di trigger sarà possibile visionare i nodi monitorati.

Impostando ad esempio un trigger su data_in 5 allo scatenarsi dell’evento nella scheda data sarà visionabile l’andamento dei segnali

Il programma permette di impostare la visualizzazione di bus di segnali con codifiche predefinite (es. unsigned decimal, Hexadecimal, etc..) o tramite tabelle mnemoniche (utile per visualizzare gli stati) e contiene altre funzioni che lasciamo scoprire al lettore.

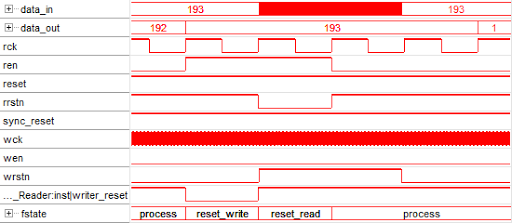

Analizziamo adesso tramite questo potente strumento il nostro design:

Alla pressione del pulsante di reset lo stato iniziale passa a wait sul fronte di salita di rck

Lo stato dopo 0.1ms passa a reset_write, il puntatore di scrittura della memoria viene azzerato tramite writer_reset che nell’entità AL422B_Writer porta wrstn al livello logico basso per attivare il reset (in questo caso già al livello basso). La scrittura viene abilitata e finito il reset potrà iniziare.

Al fronte di rck successivo lo stato passa a reset_read per l’azzeramento del puntatore di lettura della memoria tramite il segnale rrstn. Il segnale wrstn sincronizzato col dominio di clock wck viene portato al livello logico alto tramite il segnale writer_reset, sincronizzato col dominio di clock rck. Inizia la scrittura progressiva dei numeri nella memoria tramite il bus data_in. Il primo fronte di salite wck dopo il reset non comporta la memorizzazione del numero, il numero 0 non sarà quindi scritto in memoria (vedi datasheet AL422-15 Write Cycle Timing)

Al fronte di rck successivo lo stato passa a process, il segnale rrstn di reset di lettura della memoria viene disabilitato ed inizia la lettura della memoria dopo il ciclo disabilitato (vedi datasheet AL422-14 Read Cycle Timing). In data_out è possibile vedere i dati correttamente letti dalla memoria che iniziano dal valore 1 e progrediscono fino al valore 192 dopodiché la macchina a stati passa a reset_write

Nello stato reset_write il bus data_out assume il valore 193 in quanto la disabilitazione della lettura tramite il segnale ren ha effetto dal ciclo successivo (vedi datasheet AL422-14 Read Cycle Timing). Come visto dal diagramma di stato lo stato passa poi nuovamente a reset_read e a process ripetendo la scrittura / lettura della memoria

Dopo un’ispezione manuale è possibile constare che in prima approssimazione il chip AL422B funziona correttamente e sarà possibile utilizzarlo con maggiore sicurezza anche con microcontrollori lenti senza scomodare facilmente un analizzatore di stati logici reale.

Scarica il progetto analizzato nell’articolo

Nota: Il progetto scaricabile utilizza la scheda di sviluppo EP2C5 Mini Board, cambiare il dispositivo ed i pin con le impostazioni della scheda di sviluppo utilizzata