Un campo promettente per le FPGA è sicuramente l’elaborazione di flussi video in tempo reale (anche detta elaborazione di immagini). Sebbene le schede grafiche diventino sempre più potenti sotto molti punti di vista, pensiamo a settori come l’automotive dove tematiche come la guida automatica o sistemi Advanced Driver Assistance Systems (ADAS) sono sempre di maggiore attualità. I requisiti sono bassi consumi energetici, elaborazione in tempo reale e riprogrammabilità; in scenari come questo l’utilizzo delle logiche programmabili comporta, sopratutto riguardo ai consumi, grandi vantaggi.

Il primo passo di qualsiasi sistema di visione è l’acquisizione dell’immagine da elaborare, vediamo come è possibile compiere questo passo con la scheda FPGA DE0-Nano ed il modulo Digital Camera D8M-GPIO di Terasic, evoluzione per certi versi del modulo D5M. Nell’immagine seguente è mostrato a sinistra il modulo collegato alla scheda ed a destra la vista frontale del modulo.

Abbiamo già parlato della DE0-Nano in diverse occasioni, vediamo adesso cosa ci offre il D8M.

Architettura

Facendo un rapido calcolo, la quantità di dati generata da un sensore d’immagine a 30 fps e piena risoluzione (8 MP) è di: 3264 x 2448 pixel x 30 fps x 10 bit / pixel = 2.397.081.600 bit/s = 2,23 Gbps a cui si aggiungono in realtà altri dati per la sincronizzazione (overhead LVDS, segnali HSYNC, VSYNC, etc...). E’ facilmente intuibile come problematiche di integrità dei segnali non siano da porre in secondo piano.

Il sensore CMOS vista la grande quantità di dati che genera, comunica tramite 4 linee con standard elettrico LVDS (Low-voltage differential signaling) ad alta velocità, ogni linea infatti può trasferire fino a 1.2 Gbps. Il sensore supporta inoltre lo standard MIPI CSI-2 che indica come interpretare in dati i segnali elettrici.

Per semplificare il collegamento con la FPGA il modulo converte i segnali LVDS in segnali paralleli tramite un integrato TC358748XBG di Toshiba, visibile al centro della scheda. Il convertitore supporta un uscita parallela con frequenza fino a 100 MHz e una certa flessibilità, necessita però dell’appropriata programmazione.

NB: L’integrato convertitore supporta fino a 1 Gbps per linea e ha alcune limitazioni legate alla quantità di memoria FIFO interna al chip, non sarà quindi possibile raggiungere 8 MP a 30 fps ma più verosimilmente circa 2/4 fps. A risoluzioni minori sarà comunque possibile raggiungere frame-rate più elevati.

E’ di lato mostrata l’architettura del modulo D8M dove è anche possibile osservare che sia il convertitore sia il sensore CMOS dispongono di un’interfaccia di controllo I2C.

Sistema di messa a fuoco

Non è evidenziato nello schema precedente ma l’interfaccia I2C è utilizzata anche per controllare tramite l’integrato VM149C un piccolo motore VCM (Voice Coil Motor) che serve a regolare la messa a fuoco spostando la posizione della lente e quindi la distanza di quest’ultima dal sensore.

Curiosità: Il nome Voice Coil Motor proviene dalle sue prime applicazioni, la vibrazione del cono di carta degli altoparlanti.

Questo tipo di motore è molto semplice e la lo spostamento generato è proporzionale al flusso di corrente che attraversa la bobina del motore, per questo l’integrato è un driver a corrente costante. L’accuratezza nel posizionamento di questo tipo di motori può essere molto elevata, anche inferiore al micron. E’ di seguito riportato lo schema di funzionamento del VM149C:

Analizzando “in linea” le immagini ottenute è possibile creare un sistema di messa a fuoco automatica, nei reference design di Terasic è possibile trovare un esempio di semplice autofocus scritto in Verilog, anche se purtroppo non è documentato molto bene.

Sistema ottico

Per quanto riguarda la lente, elemento spesso sottovalutato ma molto importante in un sistema di acquisizione immagini, le caratteristiche principali riportate sono:

| Lens Type | |

| Effective Focal Lenght (EFL) | 3.37 mm |

| F-number | 2.8 |

| Distorsion | < 1% |

| Lens Module Dimensions | 8.5 x 8.5 x 5.4 mm |

Essendo il sensore CMOS da 1/3.2 di pollice la lente risulta il collo di bottiglia del sistema per ottenere immagini di qualità superiore, è comunque una qualità accettabile in svariate applicazioni.

UPDATE: Dopo aver segnalato il problema al produttore è stato corretto il datasheet cambiando il tipo di lente da 1/4 di pollice a 1/3.2 pollici. Kailaptech ha motivato il cambiamento di specifiche come errore di battitura. Ci è stato inoltre riportato da Terasic che il modulo include un filtro infrarosso (IR filter) a 650nm.

Dato che: F-number = Focal Lenght / Aperture Diameter abbiamo 2.8 = 3.37 / Aperture Diameter da cui ricaviamo un diametro di apertura di 1.2 mm che corrisponde effettivamente alla dimensione dell’apertura fisica della lente.

La profondità di campo (Depth of View) risulta limitata essendo proporzionale all’F-number, le immagini saranno però più luminose rispetto ad F-number maggiori in quanto la quantità di luce entrante sarà maggiore.

La lunghezza focale (Focal Lenght) molto ridotta permette un angolo di campo (o Angle of View) molto elevato, la lente abbinata al sensore OV8865 permette una visuale di circa 70° da datasheet. Il perché è facilmente intuibile dal seguente schema:

La lente ed il sensore sono in realtà a loro volta un modulo con identificativo JAL-OV8865-A898B con tanto di connettore, è quindi possibile sostituire questo modulo in caso di necessità, fermo restando che il nuovo modulo dovrà essere per forza di cosa pin-to-pin compatibile.

Sensore CMOS

Il sensore OV8865 è, come tutti i sensori d’immagine moderni, un oggetto relativamente complesso, vediamo alcune delle caratteristiche principali:

| Active array size | 3264 x 2448 |

| Lens Size | 1/3.2 inch |

| Pixel Size | 1.4 um x 1.4 um |

| Output format | 10-bit RAW (BG/GR Bayer pattern) |

| Sensitivity | 940 mV/Lux-sec |

| Dynamic Range | 68.8 dB |

| Scan mode | Progressive (Electronic Rolling Shutter) |

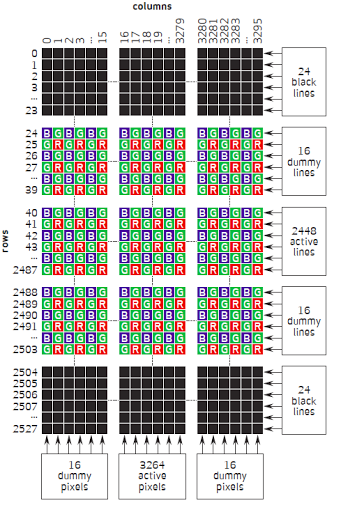

La risoluzione è un parametro abbastanza intuitivo, è il numero di pixel attivi che possiamo ottenere, in questo caso 8 MegaPixel. In realtà il sensore presenta anche dei pixel otticamente isolati che leggeranno quindi sempre il valore corrispondente al valore nero. Questo in poche parole serve per determinare l’eventuale rumore a cui sono soggetti i pixel e rimuoverlo dai pixel attivi.

La dimensione del sensore, in questo caso 1/3.2 pollici, influenza direttamente la dimensione e quindi la capacità di raccogliere la luce dei pixel. Non è chiaramente comparabile con sensori full-frame di macchine reflex ma è comunque già una dimensione utilizzata su sensori di smartphone di fascia alta.

Il sensore utilizza il pattern di Bayer, ovvero davanti ad ogni pixel è presente un filtro ottico per far passare solamente la luce di un determinato colore secondo uno schema che alterna linee con sequenze di Blu/Verde a righe con sequenze Verde/Rosso.

L’immagine originale prima della demosaicizzazione è quindi un’immagine dove la posizione di ogni pixel e la luminosità ne determinano il colore. Essendo i pixel verdi doppi rispetto ai pixel rossi e blu le immagini RAW risultano di tonalità molto verde. Ogni pixel è rappresentato da 10 bit corrispondenti alla luminosità, il colore nell’immagine finale viene stimato grazie ad un algoritmo di demosaicizzazione che può consistere in una semplice interpolazione lineare per applicazioni a basse prestazioni oppure in algoritmi molto sofisticati per risultati migliori.

|  |

| Esempio di immagine RAW in falsi colori | Stessa immagine RAW demosaicizzata linearmente |

L’inevitabile interpolazione che consiste generalmente nel 66% dei dati di una foto digitale, causa una perdita di nitidezza (sharpness) che generalmente viene compensata tramite post-processing automatico. Recenti tecniche di post-processing lavorano prima del processo di demosaicizzazione, agendo direttamente sui pixel grezzi del sensore.

Nel caso in cui il colore non sia richiesto è possibile ottenere una maggiore sensitività utilizzando sensori in bianco e nero senza quindi il filtro di bayer che introduce, seppur minimamente, una perdita di luminosità. In alternativa è spesso necessario scegliere un sensore di dimensioni maggiori se non è possibile modificare l’illuminazione o il sistema ottico.

Continuando nell’analisi delle caratteristiche è possibile notare una gamma dinamica di 68.8 dB, simile ai sensori degli smartphone di qualche anno fa e non comparabile coi sensori più avanzati HDR (High Dynamic Range) attuali che possono raggiungere 90 dB. Ad ogni modo è capace di cogliere buone immagini in condizioni di illuminazione adeguata.

La scansione dell’immagine avviene riga per riga, l’immagine non è quindi letta tutta contemporaneamente e in caso di movimenti molto veloci può sussistere un artefatto del movimento. Questa modalità è chiamata Electronic Rolling Shutter, è elettronica in quanto non è presente un otturatore meccanico e si differenzia dal Global Shutter per la sua lettura progressiva.

Vedremo più avanti altre caratteristiche e funzionalità offerte da questo sensore, così come interfacciarlo nella pratica alla FPGA.

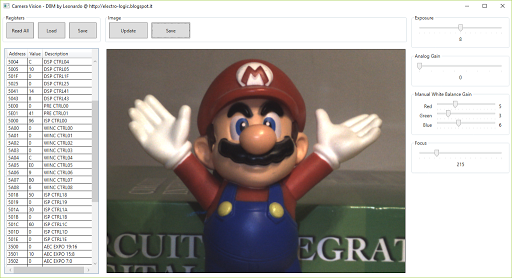

Per concludere questa panoramica vi lascio un immagine del software disponibile sul mio GitHub (‘ultima versione del software potrebbe variare rispetto alla schermata mostrata) per gestire il modulo D8M collegato alla DE0-Nano dal PC tramite JTAG. Il programma, assieme al design FPGA, sarà disponibile anche per altre schede di sviluppo come la BeMicro CV A9 e la DE1-SoC e permetterà di provare numerose impostazioni del sensore in modo semplice e veloce senza richiedere il collegamento ad uno schermo esterno VGA o HDMI, interfacce non disponibili tra l’altro su tutte le schede di sviluppo.

Alla prossima.

UPDATE: Ecco alcune foto di una Dahlia a risoluzione 1600x900 (1.4 MP) scattate con la D8M ed il progetto di cui parleremo prossimamente nel blog, la curva del blu è stata leggermente corretta con Gimp per rendere maggiormente acceso il giallo ed una foto è stata leggermente ritagliata. Facendo click sulle foto è possibile vederle a piena risoluzione.

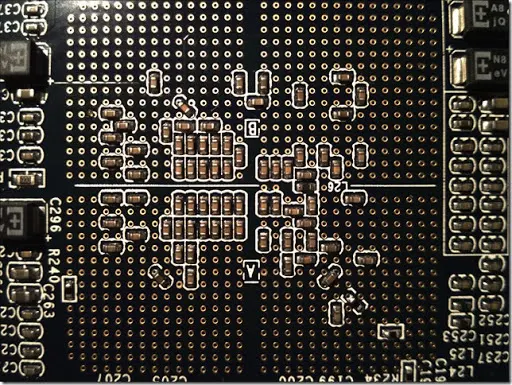

UPDATE: Ecco un ulteriore foto, anche se forse non perfettamente a fuoco. Un dettaglio del bottom della scheda DE1-SoC in prossimità dell’integrato FPGA, dove sono ben visibili i vias ed i condensatori di disaccoppiamento. La foto è stata scattata ad 8 MegaPixel con la D8M, è possibile notare una distorsione barrel dovuta all’ottica, che è comunque possibile correggere a posteriori dopo una dovuta calibrazione.