Per gli appassionati di elettronica iniziare ad utilizzare le logiche programmabili può essere un passo impegnativo.

Le schede di sviluppo FPGA più recenti offrono molte funzionalità ma necessitano la lettura di centinaia di pagine di documentazione tecnica, la conoscenza di un linguaggio di descrizione dell’hardware come VHDL o Verilog e sono in genere molto delicate. Sono spesso pensate per i professionisti del settore.

Chi non è deciso o non ha molto tempo a disposizione difficilmente farà il passo.

Con questo articolo voglio proporre un possibile percorso per gli appassionati non professionisti dell’elettronica, particolarmente amanti del DIY (Do It Yourself), per scoprire gradualmente le logiche programmabili.

Da dove partire

Prima di iniziare da un potente e costoso FPGA il consiglio è quello di può iniziare da un più semplice CPLD come l’EPM3064 della serie MAX 3000A di Altera. Sebbene un po’ datato e non permetta di realizzare veri e propri sistemi completi può aiutare all’apprendimento del workflow base di sviluppo con lo logiche programmabili.

Ecco gli svantaggi / vantaggi principali in una possibile ottica per non professionisti:

Svantaggi:

- Non compatibile con l’ultimissima versione del programma di sviluppo per logiche programmabili Quartus (gratuito nella web-edition), è possibile però utilizzare fino alla versione 13.0 SP1 installabile anche side-by-side con l’ultima versione

- Funzionalità limitate, si realizza in genere solamente semplice logica di contorno

- Programmabilità della memoria interna della CPLD limitata, garantite 100 scritture

Vantaggi:

- Datasheet di meno di 50 pagine: http://www.altera.com/literature/ds/m3000a.pdf

- Tensione di sistema compatibile coi 3.3V ed I/O compatibile coi 5V, tensioni ancora molto diffuse tra gli hobbisty

- Package disponibile in formato PLCC-44, abbinato ad un socket permette la sostituzione immediata del chip in caso di rottura, aspetto importante per chi non è professionista del settore e non vuole comprare una nuova scheda in casi mal fortuiti o di negligenza.

- Non necessita di memoria esterna

- Costo contenuto, all’incirca come un microcontrollore ad 8 bit.

Applicazioni

Alcuni possibili utilizzi della CPLD sono: sostituzione di più IC discreti di logica come ad esempio la serie 7400 con un singolo IC, microcontroller I/O expander, led driver, crosspoint switch matrices, level translator e tanti altri ancora.

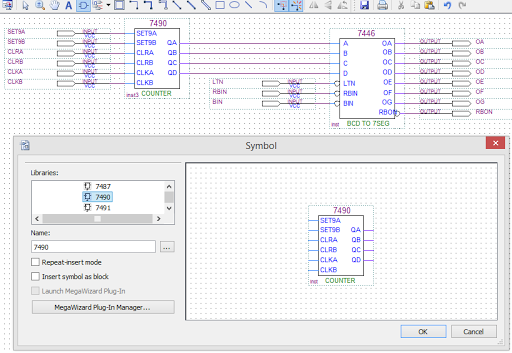

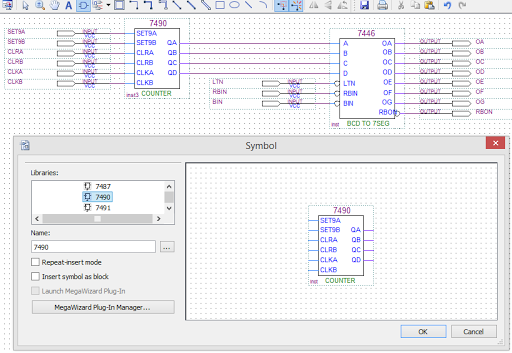

Per utilizzare la CPLD non è obbligatoriamente necessario imparare un linguaggio di descrizione dell’hardware, Quartus offre un editor visuale in cui è possibile inserire e collegare virtualmente dei componenti per sostituire velocemente ad esempio porte logiche discrete o IC della serie 7400 di cui si trova già inclusa nel programma una vasta libreria.

Per iniziare a prendere confidenza col programma partire dall’editor visuale può essere una buona idea.

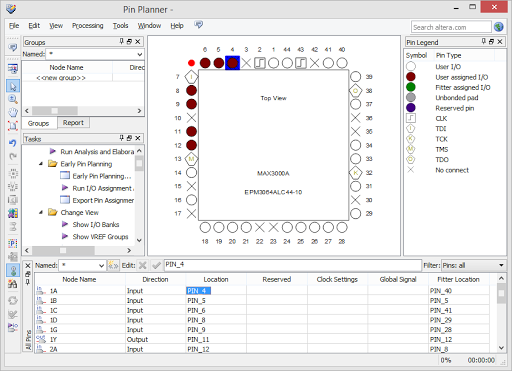

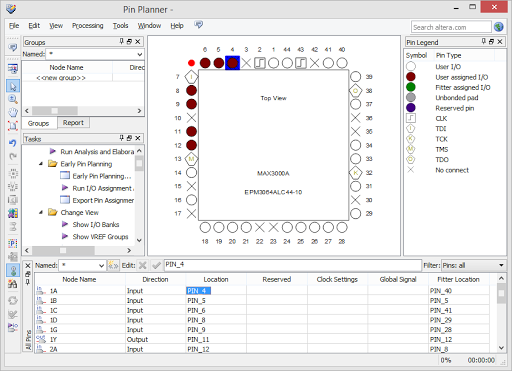

E’ inoltre possibile scegliere arbitrariamente i pin di I/O del proprio design tramite il Pin Planner di Quartus, un enorme vantaggio rispetto agli IC logici discreti tradizionali che può semplificare la realizzazione del PCB nel caso di schede specifiche per la propria applicazione

La scheda di sviluppo

Il mercato purtroppo non offre molte schede di sviluppo a basso costo e semplici per questa CPLD in involucro PLCC ed un ostacolo iniziale per gli amanti del DIY può essere progettare una scheda di sviluppo funzionante su cui imparare e poter basare successivamente i propri progetti.

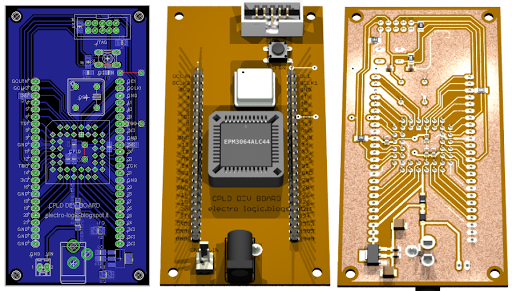

Voglio proporre in questo articolo una scheda realizzabile da appassionati con la tecnica del Toner Transfer, un reference design che permette, assieme ad un programmatore JTAG compatibile con logiche programmabili Altera reperibile su internet per pochi euro, di iniziare a sperimentare.

Lo schematico assieme al PCB, scaricabile alla fine dell’articolo, è disponibile nel formato Eagle, particolarmente amico degli hobbisty e gratuito in versione Light.

Lo schema è molto semplice, di facile comprensione a chi ha progettato anche semplici schede con microcontrollori:

- Tutti i pin della CPLD vengono esposti tramite pin header per la prototipazione rapida

- E’ presente un connettore IDC-10 per la programmazione del dispositivo tramite JTAG (come detto precedentemente è necessario il programmatore)

- Il regolatore di tensione (es. un semplice NCP1117LPST33T3G o similare in base alle necessità) fornisce una tensione stabilizzata di 3.3V, il diodo D2 è opzionale e necessario solamente se il carico capacitivo totale alimentato (CPLD + eventuali circuiti collegati alimentati) è superiore ai 50uF, nell’incertezza e visto il costo esiguo del componente è possibile aggiungerlo in ogni caso senza grossi problemi.

- Il cristallo oscillatore, montabile su socket per la sostituzione veloce, permette di realizzare successivamente design sincroni tramite la programmazione del CPLD. E’ importante che il modello scelto sia compatibile coi 3.3V, un cristallo da 50 MHz è in genere adatto per la maggior parte delle applicazioni.

- Il pulsante di Reset (opzionale) fornisce il segnale Global Clear per azzerare i flip-flop all’interno dei propri design

- E’ possibile montare sul socket indistintamente la versione PLCC dell’EPM3064A o della EPM3032A che si distingue solamente per la presenza di minori risorse logiche.

La scheda, non professionale, è pensata dando priorità alla semplicità e al basso costo.

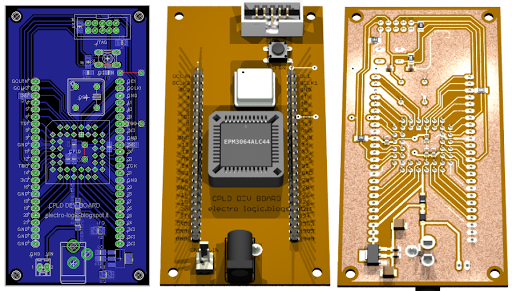

Ecco il rendering 3D della scheda, realizzato col gratuito Eagle3D

Per semplificare l’autocostruzione la scheda è stata progettata con saldature e connessioni su singola faccia, è necessario solamente realizzare tre ponticelli (collegamenti in rosso nella prima immagine) ed il collegamento sotto il socket tassativamente prima di saldare il socket stesso, altrimenti diventerà poi difficile procedere alla saldatura del ponticello.

A sinistra del pulsante di reset è presente un’aria non densamente occupata, dove in origine era presente un circuito di Pierce per permettere l’utilizzo della scheda con un più economico e facilmente disponibile quarzo. Nel rilasciare la scheda sul blog ho deciso di eliminare questa opzione in quanto non adeguatamente testata e per semplificare il tutto. E’ possibile spostare il connettore JTAG accanto al pulsante e rendere la scheda più compatta o inserire qualche componente utile in tale posizione in base alle esigenze.

Le piste sono larghe anche 10 mils, è quindi necessario utilizzare correttamente la tecnica del toner transfer per creare la scheda senza errori e frustrazioni, stampare tramite laser ad una risoluzione di almeno 1200 DPI su un supporto adeguato ed utilizzare un laminatore (o plastificatore) se non si ottengono buoni risultati con altri metodi.

E’ stato fatto uso di diversi componenti SMD (resistenze e condensatori 1206 e 0805) di semplice saldatura anche con attrezzature non professionali, c’è da porre solamente un pochino di attenzione laddove le piste passino sotto tali componenti per evitare corti circuiti.

Nota: Il PCB necessita di parecchi fori (131), è possibile però modificare senza grandissimi sforzi la scheda sostituendo tutti i componenti foro passante con equivalenti SMD, il socket PLCC smd necessita però di attrezzature in genere non alla portata dell’hobbista.

Il regolatore di tensione può necessitare di un dissipatore o di una maggiore area di dissipazione su PCB, in base alla tensione di ingresso e al consumo totale del circuito. Una stima del consumo precisa può essere fatta tramite lo strumento PowerPlay di Quartus in base al proprio design, dal datasheet il grafico del consumo tipico della CPLD è il seguente:

Dove è possibile notare come a frequenze maggiori corrispondano consumi maggiori.

Alternative

Oltre ad Altera esistono anche altri produttori di CPLD tra cui i principali Xilinx e Lattice Semiconductor.

Un ringraziamento infine all’amico Pelletta per aver collaborato allo sbroglio del PCB, realizzato e testato la scheda.

Scarica lo schema e la board

Buon divertimento con le logiche programmabili