Per migliorare l’affidabilità, le prestazioni e l’utilizzo delle risorse logiche nei nostri design, bisogna praticare una buona metodologia e capire come evitare le violazioni delle regole o linee guida raccomandate da Altera o comunque dal produttore del nostro dispositivo.

Quartus ci offre lo strumento Design Assistant per controllare la violazione delle regole e l’aderenza del nostro progetto alle linee guida di Altera.

Dopo aver compilato il nostro progetto HelloHw sviluppato negli articoli precedenti ed arricchito con un testbench scegliamo dal menù Processing / Start il comando Start Design Assistant.

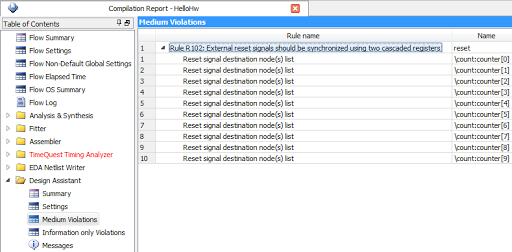

Comparirà tra i Report la cartella Design Assistant contenente le violazioni del nostro progetto, scegliendo Medium Violations notiamo che non viene rispettata una regola di media criticità mentre scegliendo Information only Violations notiamo diverse violazioni più che altro informative relative al fan-out che non presentano però criticità.

La violazione di media criticità come mostrato dal report è relativa alla regola:

Rule R102: External reset signals should be synchronized using two cascaded registers

Incontriamo questo problema perché la nostra entità HelloHw prevedeva un segnale di ingresso reset gestito in modo asincrono rispetto al segnale clock e mappato direttamente ad un pin esterno della FPGA.

Questa situazione può però portare ad un problema di metastabilità se il reset, che può avvenire in qualsiasi momento in quanto il pin esterno è collegato ad un pulsante, avviene violando il setup o l’hold time dei flip-flop collegati al reset. Nel caso di porte asincrone (es. reset asincrono del flip-flop) questi tempi vengono più propriamenti chiamati recovery e removal time.

La probabilità di metastabilità non è in questo caso elevatissima, vedremo come calcolarla successivamente, per questo nell’introduzione a Quartus per non complicare l’esempio non è stata inizialmente presa in considerazione. Per un design affidabile è bene però affrontare questo argomento.

I flip-flop seppur non definiti esplicitamente vengono generati per realizzare il registro del contatore, sotto è riportata la vista RTL del circuito come visto in un articolo precedente.

La metastabilità può essere pensata come uno stato incerto che dopo un certo periodo di tempo detto tempo di risoluzione dove l’uscita può oscillare, si stabilizza ad un valore casuale. Una situazione non desiderata che può portare a problemi ed errori nei nostri design. L’incertezza può essere pensata come ad uno stato instabile, un palla nella cima di una collina molto ripida che alla minima perturbazione può andare casualmente al vecchio valore o ad un nuovo valore (quindi 0 o 1)

Sotto un esempio di metastabilità, l’ingresso viola il recovery time cambiando il proprio valore troppo vicino al fronte di salita del clock e comporta un uscita metastabile ovvero un valore elettrico intermedio tra i valori relativi ai due stati logici che può risolversi successivamente nel valore logico 1 o 0.

Il Design Assistant ci avverte quindi di una situazione pericolosa che a progettisti in erba può facilmente sfuggire, la soluzione al problema consiste, come suggerito dalla descrizione della violazione, nell’utilizzare due flip-flop in cascata per sincronizzare la de-asserzione del reset.

Esistono diverse implementazioni della soluzione con diversi vantaggi /svantaggi, vediamo con un esempio concreto una soluzione molto affidabile: l’asserzione asincrona / de-asserzione sincrona tramite il circuito:

In realtà la soluzione non risolve in termini assoluti il problema che nelle simulazioni verrà riportato a meno di non impostare tempi di recovery e removal time nulli, risolve però il problemi in termini probabilistici, la probabilità che il secondo flip-flop presenti un uscita metastabile che si propaga nel resto del circuito diventa molto bassa come vedremo maggiormente in dettaglio in un prossimo articolo. Ad ogni modo è utile sapere che è possibile aggiungere ulteriori flip-flop per rendere piccola a piacere la probabilità di metastabilità in uscita.

Il codice VHDL per realizzare un modulo di reset sincrono è presto fatto:

Dove q0 sarà il segnale interno di uscita del primo flip-flop D.

L’utilizzo del modulo sarà abbastanza semplice, basterà interporlo al segnale di reset proveniente dal mondo esterno alla FPGA per generare un segnale di reset sincrono come illustrato dal seguente schema a blocchi.

Così facendo la violazione scomparirà dal report.

Concludendo l’utilità del Design Assistant è molto elevata e seppur non risolva in automatico i problemi la loro consapevolezza è sempre il primo passo verso la risoluzione.

![rtl opt[4] rtl opt[4]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEgph3Ic5r3QguaGhRaJLk3uaW5OQiQr_tA1EzO2l9Y-wOIfgcZs8G7zsV0FKIh91XZFljLOVOmmbKu1FrAq4ykqwgcBxVd7XiUP5haehGxJiU64uUMUiRovye3HrsT81WWFplNA1jBNb8Q/rw/?imgmax=800)

Nessun commento:

Posta un commento