Scopriamo in questo articolo il flessibile sistema di clock dell’AVR XMega A4U che ricordiamo essere molto simile agli altri XMega e vediamo come configurarlo con semplicità grazie al modulo ASF System Clock Control che abbiamo aggiunto al nostro progetto ed analizzato nelle precedenti puntate.

Per chi volesse scaricare il progetto Atmel Studio creato fino ad ora: progetto_introduzione_ASF_3

Come detto nell’articolo precedente, dopo il reset (quindi all’avvio) il dispositivo partirà sempre dall’oscillatore interno da 2 MHz dopodiché sarà possibile cambiare a runtime attraverso il nostro firmware i vari clock di sistema.

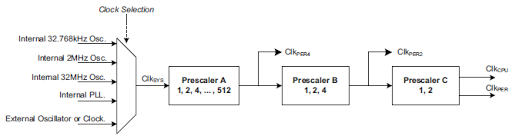

Vediamo adesso uno schema tratto dal datasheet del microcontrollore che riassume bene cosa ci offre relativamente ai clock:

Inizialmente si può essere spaventati da tante opzioni e sigle, una domanda spesso posta dagli esordienti è “ma non bastava un semplice clock generale?”

Il microcontrollore dispone di molte periferiche che lavorano tipicamente a velocità diverse dalla CPU:

- il modulo Brown-out che rileva eventuali cali di alimentazione azionando il reset ed il Timer Watchdog che permette la rilevazione di blocchi del firmware lavorano ad 1 kHz generato a partire da un clock a 32 kHz

- il Contatore Real Time (RTC) che permette di tenere traccia del tempo lavora tipicamente a 1024 kHz ma può lavorare con maggiore risoluzione (maggiore di 1ms) a 32.768 kHz

- il modulo USB richiede un clock minimo di 6 MHz per lavorare in low speed ed almeno 48 MHz per la modalità full speed

- le periferiche come il controller DMA, il sistema di eventi, il controller delle interruzioni e la RAM hanno un clock impostabile chiamato clkPER

- il modulo EBI (External Bus Interface) usato per collegare memorie esterne come SRAM e SDRAM o periferiche come display LCD mappati in memoria lavora ad un clock clkPER2 veloce fino al doppio rispetto alle periferiche. Il modulo è presente solo su alcuni package, in generale con un elevato numero di pin, non è presente sulla nostra scheda di sviluppo EWS ATXMega32A4U.

- il modulo Hi-Res ha clock clkPER4 fino al quadruplo rispetto alle periferiche, è utilizzato per generare forme d’onda ad alta risoluzione

Adesso il perché il micro ha diversi clock configurabili può risultare più chiaro, in alcuni casi la scelta permetterà di privilegiare la velocità e la precisione in altri il risparmio energetico e minori possibilità di interferenze elettromagnetiche (EMI). Questa panoramica ci ha dato inoltre un’idea di cosa fanno alcune periferiche del micro.

I clock delle periferiche clkPER4, clkPER2, clkPER e della CPU e memoria EEPROM non volatile clkCPU sono generati a partire da clkSYS che è selezionato direttamente da una delle varie sorgenti di clock, dopodiché come è possibile vedere dal seguente schema può essere diviso diverse volte da vari Prescaler configurabili per generare le altre frequenze.

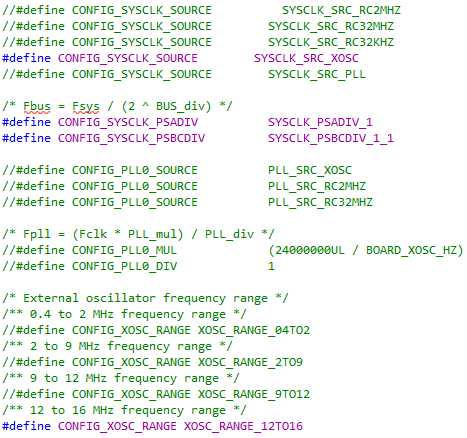

Dopo questa introduzione al sistema di clock comprendere il file di configurazione conf_clock.h (sotto riportato) del modulo ASF System Clock Control sarà senz’altro più semplice:

Tralasciamo per il momento le voci relative al PLL che vedremo in un prossimo articolo.

Impostiamo adesso come sorgente del clock di sistema (clkSYS) l’oscillatore esterno da 12 MHz presente sulla scheda, per fare ciò dobbiamo commentare la prima riga (o comunque le altre definizioni di CONFIG_SYSCLK_SOURCE) e de-commentare

#define CONFIG_SYSCLK_SOURCE SYSCLK_SRC_XOSC

Per specificare la frequenza è necessario de-commentare

#define CONFIG_XOSC_RANGE XOSC_RANGE_12TO16

Se avessimo avuto un oscillatore non compreso tra 12 e 16 MHz avremmo dovuto scegliere la corrispondente definizione.

Possiamo notare che il Prescaler A ed il Prescaler B e C sono impostati ad 1 tramite le righe

#define CONFIG_SYSCLK_PSADIV SYSCLK_PSADIV_1#define CONFIG_SYSCLK_PSBCDIV SYSCLK_PSBCDIV_1_1

In particolare la prima definizione si occupa di impostare il Prescaler A e la seconda i Prescaler B e C, questo poiché i Prescaler B e C sono dipendenti tra loro nella scelta dei valori di divisione.

Nel file di intestazione asf\common\services\clock\xmega\sysclk.h sono presenti i valori che possiamo assegnare alle due definizioni

Per raggiungere questo file ricordo che possiamo andare alla definizione ad esempio di SYSCLK_PSADIV_1 e tramite il comando Goto implementation accessibile tramite click destro sulla parola verrà aperto il file interessato che contiene le nostre definizioni.

Con questa configurazione il nostro micro, la cpu e tutte le sue periferiche, viaggeranno a 12 MHz.

Impostando invece ad esempio

#define CONFIG_SYSCLK_PSBCDIV SYSCLK_PSBCDIV_4_1

Avremmo avuto il Prescaler B a 4 e gli altri ad 1 avendo così: clkSYS e clkPER4 a 12 MHz ma clkPER2, clkPER e clkCPU a 3 MHz, in parole povere il modulo Hi-Res ad una frequenza 4 volte superiore rispetto alla CPU ed alle periferiche.

Nessun commento:

Posta un commento