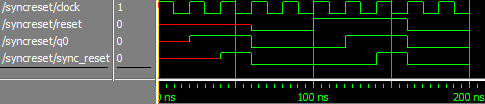

Abbiamo visto nel precedente articolo cos’è la metastabilità e come minimizzare la sua propagazione tramite una catena di registri di sincronizzazione sotto riportata per comodità di lettura:

I flip-flop realizzano la asserzione asincrona / de-asserzione sincrona.

Un eventuale reset asincrono che viola i tempi di recovery e removal potrà però causare metastabilità nel primo flip-flop provocandone l’uscita q0 ad un valore intermedio tra 1 o 0 e assestandosi poi ad un valore logico casuale.

Se l’ingresso asincrono (il segnale reset) rimane però stabile, al successivo fronte di salita del clock q0 assumerà il valore dell’ingresso e al periodo di clock successivo sarà propagato all’uscita sync_reset.

Se la metastabilità non si risolve prima del fronte di clock successivo potrebbe propagarsi nel secondo flip-flop (quindi all’uscita), la probabilità è però minore tanto minore è la frequenza del clock.

La soluzione circuitale è pertanto valida se il segnale asincrono è sovra-campionato dai flip-flop prima di una sua variazione ed è ammissibile un ritardo nel segnale di uscita non costante.

Ipotizzando un ingresso che non causi metastabilità per semplicità il segnale di uscita (sync_reset) avrà un ritardo di 2 periodi di clock per passare da 0 a 1 mentre solamente un ritardo legato al tempo di reset asincrono del flip-flop nel passare da 1 a 0. Per questo si dice che realizzano la asserzione asincrona / de-asserzione sincrona.

E’ da notare dalla simulazione che se il segnale reset sarà indeterminato l’uscita assumerà il valore 1 logico sempre dopo 2 periodi di clock.

Il sovra-campionamento è necessario in quanto se il segnale reset cambiasse prima del fronte di clock successivo e tornasse quindi a 0 e la metastabilità si risolvesse con il solito valore (valore precedente), il valore del segnale reset non sarebbe mai presentato in uscita.

Il circuito visto non è quindi sempre applicabile in qualunque situazione ed è di fondamentale importanza la stabilità del valore di ingresso rispetto al periodo del clock, è però adatto per gestire l’ingresso proveniente da un segnale di reset filtrato preventivamente da anti-rimbalzo (debounced) come sulla scheda DE0-Nano.

La probabilità di propagazione ai successivi flip-flop e quindi all’uscita della metastabilità è calcolabili in termini di MTBF (Mean Time Between Failures), tempo medio tra guasti dovuti alla metastabilità, che Quartus ci permette di calcolare agevolmente.

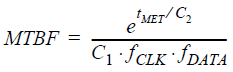

La formula utilizzata è la seguente:

con C1 e C2 costanti dipendenti dal dispositivo (es. processo produttivo) e dalle operazioni operative (es. temperatura), fCLK è la frequenza del clock utilizzato per ricevere il segnale asincrono, fDATA la frequenza del segnale asincrono in ingresso. tMET è il tempo a disposizione del segnale per risolvere la metastabilità.

La formula ci indica che possiamo esponenzialmente migliorare la situazione aumentando il tMET e linearmente riducendo fCLK o fDATA.

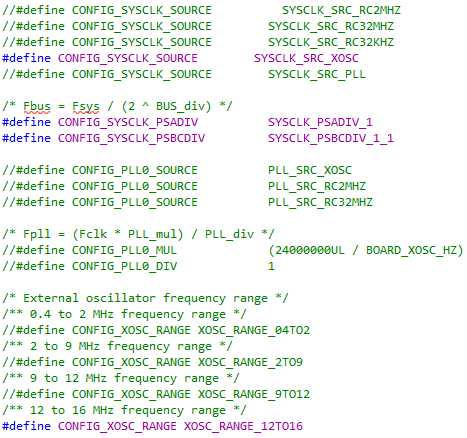

Specifichiamo tramite un file SDC (mostrato sotto) la frequenza del nostro clock (fCLK nella formula)

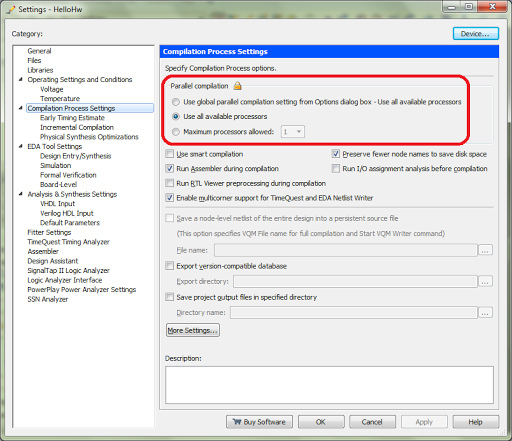

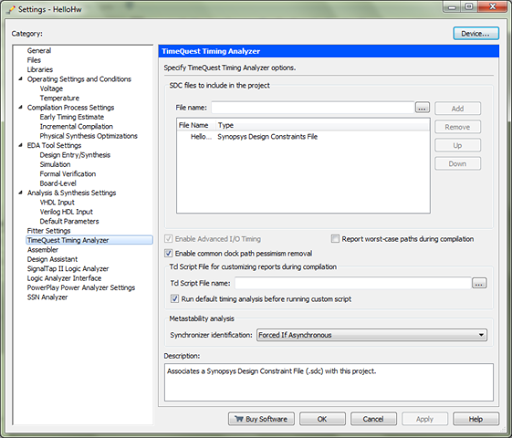

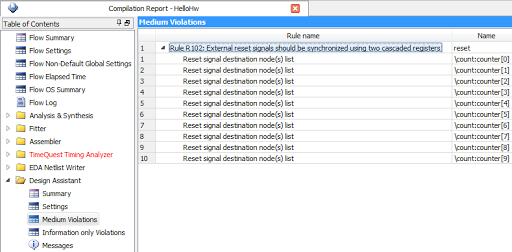

Abilitiamo l’analisi della metastabilità tramite il menù Assignments / Settings ed impostando Synchronizer identification a Forced If Asynchronous, di default Quartus è abbastanza conservativo e l’identificazione è disattivata

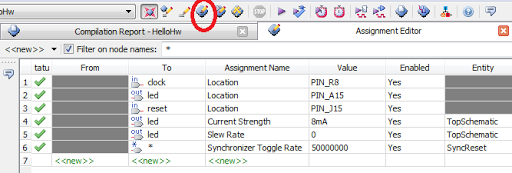

Apriamo adesso Assignments / Assignment Editor ed impostiamo per l’analisi l’analogo di fDATA nella formula, ovvero la frequenza del segnale di ingresso. Aggiungiamo una nuova voce scegliendo To *, Assignment Name Synchronizer Toggle Rate ed impostiamola a 50 milioni per simulare un ingresso commutante a 50 MHz. Questo valore può risultare eccessivo per un segnale di reset ma ci porrà sul lato sicuro e permetterà di mostrare le differenze di MTFB altrimenti non percettibili.

Avviamo adesso una compilazione completa del design ed apriamo il Metastability Report sotto la cartella TimeQuest Timing Analyzer del report della compilazione.

Notiamo che con un clock di 50 MHz il MTBF tipico stimato è di oltre 1 miliardo di anni, un risultato niente male.

Il tMET si può leggere dalla quarta riga è di 19.246 ns, molto elevato e comporta robustezza al nostro design.

Aumentando il clock a 400 MHz e ricompilando il MTBF si riduce notevolmente a 28.3 anni, la nuova constraints con le impostazioni di default del fitter non è soddisfabile è genera dei Warning Timing requirements not met durante la compilazione, il tutto comporterà fragilità nel design

Il tempo di assestamento disponibile in questo caso notiamo essere di 1.439 ns, molto inferiore al caso precedente.

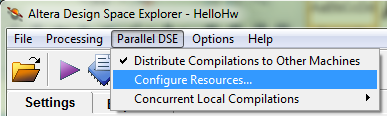

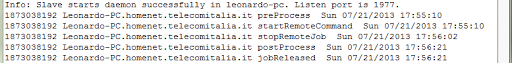

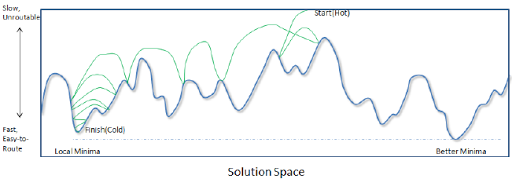

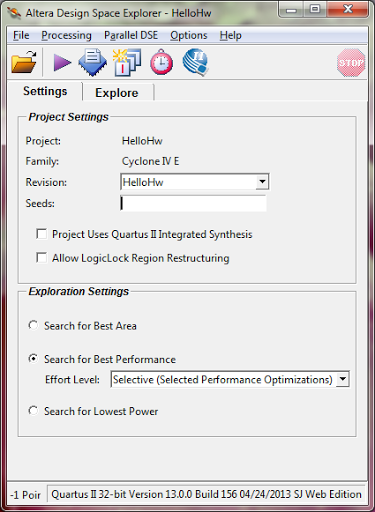

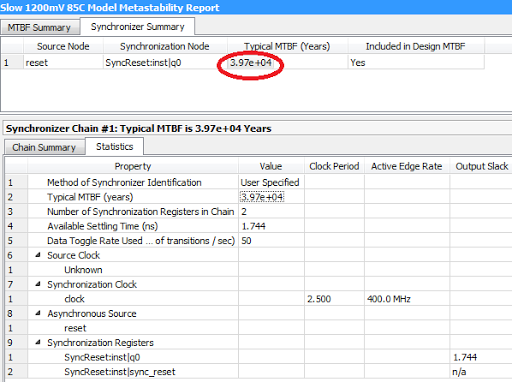

E’ possibile notare come modificando i parametri del progetto per una sintesi più aggressiva ed utilizzando Design Space Explorer di cui abbiamo parlato in un articolo precedente, ci si avvicini maggiormente a soddisfare la frequenza di 400 MHz (ancora senza soddisfarla in questo caso) ed il MTBF cambi sensibilmente passando a 39.700 anni, una variazione di soli 0.305 ns pari a circa il 21% del valore precedente nell’ Avaible Settling Time comporta dunque una situazione molto diversa come era intuibile dalla formula dell’MTBF.

Altera consiglia di utilizzare un minimo di tre flip-flop per sincronizzare segnali asincroni proprio perché il tempo di assestamento è uno strumento fondamentale per evitare la metastabilità.

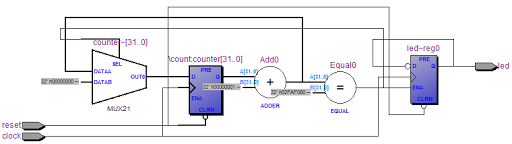

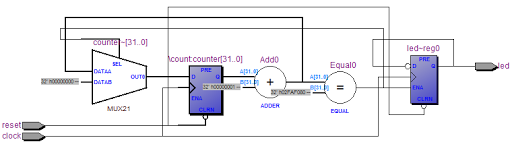

![sync_reset[4] sync_reset[4]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEiP6qlFr5fLFnfIY0vo1BY2zhPhKP0Y4qghDqtvsbTgNhAo2QkQsxXN6yJO_Pbe0TwiWgpw6CU7RY5Ag63F8tvkqiWxem9CzZpRdL5-ztmSggdKi-fsN2OiyDiFi-FkexrJndjlMzw-R-A/rw/?imgmax=800)

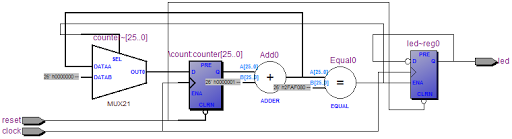

![rtl opt[4] rtl opt[4]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEgph3Ic5r3QguaGhRaJLk3uaW5OQiQr_tA1EzO2l9Y-wOIfgcZs8G7zsV0FKIh91XZFljLOVOmmbKu1FrAq4ykqwgcBxVd7XiUP5haehGxJiU64uUMUiRovye3HrsT81WWFplNA1jBNb8Q/rw/?imgmax=800)